### **SKARAB**

AGILE 40 GBE NETWORKED FPGA COMPUTE/INSTRUMENT PLATFORM

Designed and Manufactured by Peralex Electronics

Distributed worldwide by Cyntony

### SKARAB IS READY FOR YOUR RESEARCH TODAY

- Board Support Package (BSP) on Github

- SKA-SA software uses open source Apache Version 2 license

- CASPER Listserv development support, led by SKA-SA

- Over 100 SKARAB systems delivered to SKA-SA by Peralex

- Mature, fully qualified and shipping

- FPGA board, power supply, cooling in 1U enclosure

- 4 x 40 GbE QSFP+ mezzanine card

- 4 GB Hybrid Memory Cube mezzanine card

- New 3 GSPS 14-bit ADC mezzanine card

- Cyntony distributes worldwide

# + HOW WILL YOU USE SKARAB? AS A...

**SPECTROMETER**

**BEAMFORMER**

**RADAR**

**NEW GIZMO?**

### SKARAB

Extreme FPGA computing

Real-time reconfiguration

Massively networkable

Wideband A/D conversion

Highly power efficient

Concept by SKA-SA

Design and Manufacture by

Peralex Electronics

### DESIGN AND VERIFICATION

- Peralex won RSA tender deliver 300 SKARABs for MeerKAT

- Extensive signal integrity analysis and verification

- 10.3125 Gbps over 7m on 128 links.

- CFD and real-world thermal analyses

- MTBF analysis fed back into design to maximize reliability

- 110,000 hours at 44 degC

- Thorough environmental design verification tests

- EMC/RFI, temperature, shock and vibration

### MANUFACTURING AND TEST

- Peralex assembles units and performs automated final tests

- Internal and supply chain quality management

- Optimized assembly fixtures and test harnesses

- Thermal stress screening to eliminate infant mortality

- Key components get supplier tests

- PCB delamination stress testing

- X-ray/AOI inspection of all PCB assemblies

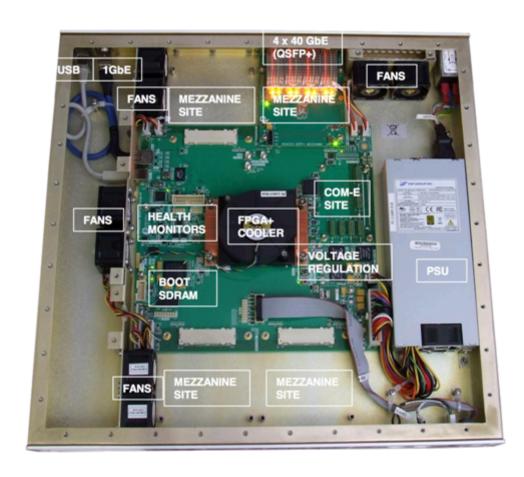

# SQUARE KILOMETER ARRAY RECONFIGURABLE APPLICATION\* BOARD

Under the hood

\*SKARAB is <u>NOT</u> application specific

### SKARAB SPECS

Xilinx Virtex 7 FPGA

XC7VX690T-2-FFG1927

693,120 logic cells

3600 DSP slices

54 Mb RAM

80 x SERDES channels

1.28 TBPS total throughput

4 x 40 GbE QSFP+

Quad 3 GSPS ADCs optional

Hybrid Memory Cube optional

COM-Express mezzanine optional

GBE management interface

Remote monitoring/shutdown

Energy efficient (45 W floor)

1U rackable form factor

5 to 40 deg C operating temp range

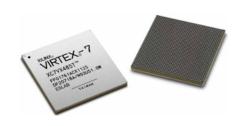

### SKARAB FPGA: VIRTEX

- 693120 Logic Cells

- 80 x SERDES

- 64 for mezzanine I/O

- 1 for COM-Express site

- 1470 x 36Kb RAM Blocks (~52 Mb)

- 3600 DSP Slices

- 1927 pins

|               |                                             | Part Number                           | XC7VX690T       |  |  |  |  |  |  |

|---------------|---------------------------------------------|---------------------------------------|-----------------|--|--|--|--|--|--|

|               | EasyPath™ (                                 | XCE7VX690T                            |                 |  |  |  |  |  |  |

| Logic         |                                             | Slices                                | 108,300         |  |  |  |  |  |  |

| _             |                                             | Logic Cells                           | 693,120         |  |  |  |  |  |  |

| Resources     |                                             | 866,400                               |                 |  |  |  |  |  |  |

| Mamani        | Maxim                                       | num Distributed RAM (Kb)              | 10,888          |  |  |  |  |  |  |

| Memory        | Block RAM,                                  | /FIFO w/ ECC (36 Kb each)             | 1,470           |  |  |  |  |  |  |

| Resources     |                                             | 52,920                                |                 |  |  |  |  |  |  |

| Clocking      |                                             | CMTs (1 MMCM + 1 PLL)                 | 20              |  |  |  |  |  |  |

| I/O Resources | N                                           | 1,000                                 |                 |  |  |  |  |  |  |

| I/O Resources | Maxi                                        | 480                                   |                 |  |  |  |  |  |  |

|               |                                             | DSP Slices                            | 3,600           |  |  |  |  |  |  |

|               |                                             | PCle® Gen2 <sup>(2)</sup>             | _               |  |  |  |  |  |  |

|               |                                             | PCIe Gen3                             | 3               |  |  |  |  |  |  |

| Integrated IP | Analog N                                    | 1                                     |                 |  |  |  |  |  |  |

| Resources     | Configu                                     | 1                                     |                 |  |  |  |  |  |  |

|               | GTX Transceive                              | _                                     |                 |  |  |  |  |  |  |

|               | GTH Transceive                              | 80                                    |                 |  |  |  |  |  |  |

|               | GTZ Transceive                              | _                                     |                 |  |  |  |  |  |  |

|               |                                             | Commercial<br>Extended <sup>(5)</sup> | -1, -2          |  |  |  |  |  |  |

| Speed Grades  |                                             | -2L, -3                               |                 |  |  |  |  |  |  |

|               |                                             | Industrial                            | -1, -2          |  |  |  |  |  |  |

|               | Package <sup>(6)</sup>                      | Dimensions (mm)                       | GTH)            |  |  |  |  |  |  |

|               | FFG1157 / FFV1157 <sup>(7)</sup>            | 35 x 35                               | 0, 600 (0, 20)  |  |  |  |  |  |  |

| Footprint     | FFG1761 / FFV1761 <sup>(7)</sup>            | 42.5 x 42.5                           | 0, 850 (0, 36)  |  |  |  |  |  |  |

| Compatible    | FHG1761                                     | 45 x 45                               |                 |  |  |  |  |  |  |

|               | FLG1925                                     | 45 x 45                               |                 |  |  |  |  |  |  |

| Footoolos     | FFG1158 / FFV1158 <sup>(7)</sup>            | 35 x 35                               | 0, 350 (0, 48)  |  |  |  |  |  |  |

| Footprint     | FFG1926                                     | 45 x 45                               | 0, 720 (0, 64)  |  |  |  |  |  |  |

| Compatible    | FLG1926                                     | 45 x 45                               | 0 (00 (0 (0)    |  |  |  |  |  |  |

| Footprint     | FFG1927 / FFV1927 <sup>(7)</sup><br>FFG1928 | 45 x 45<br>45 x 45                    | 0, 600 (0, 80)  |  |  |  |  |  |  |

| Compatible    | FFG1928<br>FLG1928                          |                                       |                 |  |  |  |  |  |  |

| Footprint     | FFG1930                                     | 45 x 45<br>45 x 45                    | 0, 1000 (0, 24) |  |  |  |  |  |  |

| Compatible    | FLG1930                                     | 45 x 45                               | 0, 1000 (0, 24) |  |  |  |  |  |  |

| Companie      | . 202000                                    | 15 / 15                               | 15              |  |  |  |  |  |  |

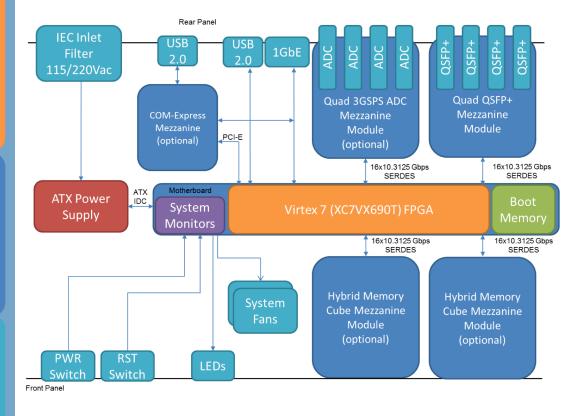

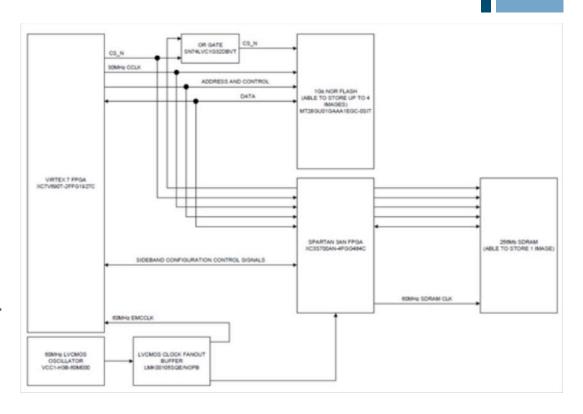

### + FPGA (RE)CONFIGURATION

- On power-up, FPGA boots from NV flash

- Can then be rebooted over 1 GbE using SDRAM-based highspeed boot mode

- Boots in < 1 second for rapid reconfiguration

### FOUR MEZZANINE SITES

- 400 pin MEG-array connectorCapable of 28 Gbps

- 16 x ~10 Gbps SERDES

- 1-Wire Interface (config PROM)

- I2C management interface

- JTAG test interface

- High speed clocks

- Power (12V, 5V, 3.3V)

|          |      |      |      |     |          | Pi Pi | NOT LAN |     |          | PMYSS LAWES PMYSS LAWES |                   |     |      |     |      |     |        | PAYON LAMES |      |     |         |      | PHYS LANET DAWN |     |      |      |      |             |      | -   | POST LAN | er. |          | P   | PORT 1.44 | 62  |      |       |       |

|----------|------|------|------|-----|----------|-------|---------|-----|----------|-------------------------|-------------------|-----|------|-----|------|-----|--------|-------------|------|-----|---------|------|-----------------|-----|------|------|------|-------------|------|-----|----------|-----|----------|-----|-----------|-----|------|-------|-------|

| 40       | 39   | 38   | 37   | 36  | 36       | 36    | 33      | 32  | 31       | 30                      | 29                | 28  | 27   | 26  | 26   | 24  | 23     | 22          | 21   | 20  | 10      | 18   | 17              | 96  | 15   | 14   | 13   | 10          | 11   | 10  | 9        |     | 2        | 6   | 5         | 4   | 3    | 2     | 1     |

| A VCC    | 6/60 | 3.79 | 100  | GND | GND      | GNO   | GND     | GND | GND      | GRO                     | GND               | GND | GNO  | GND | GND  | GND | GND    | GNO         | GND  | GND | GND     | GRO  | GND             | GND | GNO  | GND  | GND  | GND         | GND  | GND | GND      | GND | GND      | GNO | GWD       | GND | Ten  | 503.  | 50A   |

| B VCC    | GNO  | 1.00 | - 10 | GND | RDIP     | GNO   | RUP     | GND | FOUP     | GWD                     | RHP               | GND | ROOP | GND | KHP  | GND | RNP    | GND         | RICP | GND | FOUP    | GWD  | RHP             | GND | ROOP | GND  | EUP  | GND         | RNP  | GND | RUP      | GND | RDIP     | GND | RICP      | GND | 20A  |       | THIS  |

| C VCC    | GNO  | 1.79 | 200  | GNO | ROOM     | GND   | RICH    | GND | RODI     | GND                     | ROOM              | GND | ROOM | GND | RODE | GND | RODI   | GND         | RICH | GND | ROBI    | GNO  | RXXX            | GND | ROOM | GND  | ROW  | GND         | ROW  | GND | RXX      | GND | FOOM     | GNO | RHOW      | GND | AO1  |       | 100   |

| B VCC    | GNO  | 1277 |      | GND | CND      | CND   | GND     | CND | CND      | GIO                     | CND               | CND | CND  | CND | GND  | CND | CND    | CND         | GND  | CND | CND     | GIO  | CND             | CAD | GNO  | CND  | GND  | GND         | CND  | CND | GND      | CND | CND      | GND | GIO       | GND | ADI  | 189   | THE   |

| E VCC    | GND  | 1257 | 200  | GND | OPT      | GNO   | OPT     | GND | OPT      | GND                     | OPT               | GND | OPT  | GND | OPT  | GND | OPT    | GNO         | OPT  | GND | OPT     | GND  | OPT             | GND | OPT  | GND  | OPT  | GND         | OPT  | GNO | OPT      | GND | OPT      | GND | OPT       | GND | Ma   | DOT_N | Fa_E  |

| r vcc    | GNO  | 129  | 100  | GND | OPT      | CND   | OPT     | GND | OPT      | GIND                    | OPT               | CND | OPT  | CND | OPT  | GND | OPT    | CND         | OPT  | CND | OPT     | GIND | OPT             | CND | OPT  | CND  | OPT  | GND         | OPT  | CND | OPT      | CND | OPT      | GND | OPT       | GND | CND  | GIID  | GND P |

| G 50     | GND  | 1297 | 200  | GND | GND      | GNO   | GND     | GND | CND      | GND                     | GND               | GND | CND  | GND | GND  | GND | GND    | GND         | GND  | GND | GND     | GND  | GND             | GND | GND  | GND. | GND  | GND         | GND  | GND | GND      | GND | GND      | GNO | GWD       | GND | DOM  | DOM   | GND   |

| Pi Vanna | 680  | 1.79 |      | GNO | TRP      | CNO   | TXP     | GND | THE      | GNO                     | THP               | GND | TKP  | CND | TOUP | GND | DO     | CND         | TXP  | GND | TRP     | G80  | THP             | GND | TRP  | CND  | TOUR | GND         | TRP  | CNO | TXIP     | GND | THP      | GNO | TXXP      | GND | GND  | GND   | GNO   |

| Ween.    | GNO  | 1297 | 100  | GND | THN      | GNO   | TXN     | GND | TEUN     | GWD                     | THE               | GND | TION | GND | TXN  | GND | THN    | GND         | TXN  | GND | 1308    | GWD  | THRE            | GND | TION | GND  | TORN | GND         | THE  | GNO | TXN      | GND | TION     | GNO | TXX       | GND | CKIM | CKIP  | GNO   |

| * VCCH   | GIO  | 1.00 | 100  | GND | GND      | CNO   | GND     | GND | CND      | GND                     | GND               | GND | CND  | GND | GND  | GND | CND    | CND         | GND  | GND | CND     | G80  | GND             | CND | GNO  | CND  | GND  | GND         | GND  | CND | GND      | GND | CND      | GNO | GND       | GND | CND  | GIED  | GNO   |

| 40       | 25   | 38   | 37   | -26 | 38       | 34    | 33      | 32  | 31       | 30                      | 29                | 29  | 27   | 25  | 8    | 24  | 23     | 22          | 21   | 29  | 19      | 18   | 17              | 96  | 15   | 14   | 13   | 12          | - 11 | 10  | 9        |     | 7        | - 6 | 5         | 4   | - 3  | 2     | 1     |

|          |      |      |      |     | WYZZ_LAI | 6.1   |         | n   | 1972_LAI | 62                      | PROS_LANCE PROSS_ |     |      |     |      |     | H25_LA | 62          |      | -   | MIS_LAN | 69   | PRYST, LANCE    |     |      |      |      | PHTTI_LARCE |      |     |          | -   | RTT, LAN | 62  |           |     |      |       |       |

### <sup>+</sup> 4 x 40 GbE QSFP+ **MEZZANINE CARD**

- 4 x QSFP+ interfaces

- 16 x 10 Gbps SERDES

- Copper, AOC, SR & LR fiber

- 32-bit ARM μC (mgnt & boot)

- Configuration PROM

- Clock generation

- Thermal sensor

- Design/Manufacture by Peralex

## HYBRID MEMORY CUBE MEZZANINE CARD

- 4 GB Micron HMC chip

- 10 Gbps x 16 SERDES to FPGA

- Relative to DDR3/4:

- Higher bandwidth

- More energy efficient

- More parallel

- Relative to QDR SRAM & Bandwidth Engine

- Larger capacity

- Designed by SKA-SA

- Manufactured by Peralex

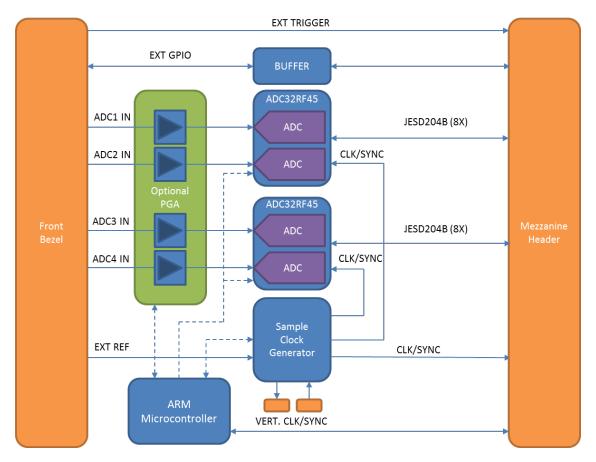

### + ADC32RF45X2 MEZZANINE

- 2/4 3 GSPS 14-bit ADC Channels

- 600 MHz BW

- 22 W power consumption at 3 GSPS

- optional PGA

- On-board digital down converters

- Two per ADC & dual band modeThree independent NCOs/DDC\*

- High perf. 3 GHz sample clock generator

- Phase synchronous DAQ across channels/boards

- Dedicated sub-system management μP

- JESD204B interface to FPGA

- Design/Manufacture by Peralex

### + ADC32RF45X2 BLOCK **DIAGRAM**

# + ADC MEZZANINE CONFIGURATION OPTIONS:

- Two ADC chip variants, one or two chips per mezzanine

- TI ADC32RF45 Full 1.5 GHz Nyquist bandwidth using DDC bypass

- TI ADC32RF80 DDC not by-passable, max BW of 600 MHz

- lower priced

- Programmable Gain Amplifier (PGA) vs balun-coupled input

- PGA gain range: ~ -6 to +15 dBm

- PGA lowers required full scale drive strength (at the expense of NF)

- Balun coupling recommended when operating at higher analog input frequencies (e.g. 2.0 GHz)

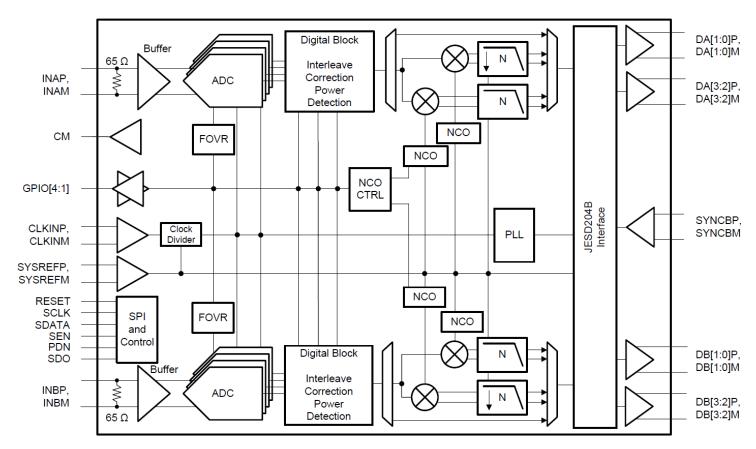

### TI ADC23RF45 CHIP SPECS

- □ Dual-Channel, 14-Bit, 3.0-GSPS ADC

- □ Input Full-Scale: 1.35 VPP

- □ RF Input Supports Up to 4.0 GHz

- On-chip 50 Ohm Input Termination

- On-chip Digital Down-Converters:

- Up to 4 DDCs (Dual-Band Mode)

- Up to 3 Independent NCOs per DDC

- On-chip Dither

- Aperture Jitter: 90 fsec

- Noise Floor: –155 dBFS/Hz

- □ Channel Isolation: 95 dB at Fin = 1.8 GHz

- Programmable On-Chip Power Detectors

- Alarm Pins for AGC Support

- On-chip Over-voltage Protection Clamp

- □ JESD204B Interface

- 4 Lanes Per Channel at 12.5 Gbps

- Support for Multi-Chip Synchronization

- □ Spectral Performance (Fin = 900 MHz, -2 dBFS)

- □ SNR: 60.9 dBFS

- □ SFDR: 67 dBc HD2, HD3

- SFDR: 77 dBc Worst Spur

- □ Spectral Performance (Fin = 1.78 GHz, –2 dBFS)

- □ SNR: 58.8 dBFS

- □ SFDR: 66 dBc HD2, HD3

- □ SFDR: 75 dBc Worst Spur

### <sup>+</sup>TI ADC32RF45 DUAL ADC **BLOCK DIAGRAM**

Copyright © 2016, Texas Instruments Incorporated

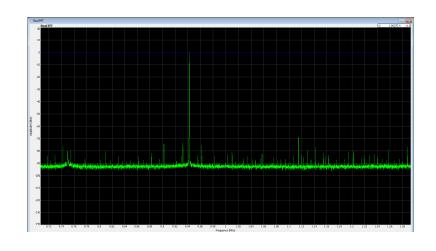

### + SKARAB ADC32RF45X2

Test Case 1:

Input Frequency: 942.5 MHz Input amplitude: -10 dBFS Sample rate: 3.0 GSPS Full Scale: 9.375 dBm DDC: Decimate-by-4

FFT: 16384 Average: 5 PGA: none

Result <<

Single-tone spurious: -71.725 dBc IMD3: 76.435 dBc @ -8dBFS FFT Noise Level: -94.125 dBm

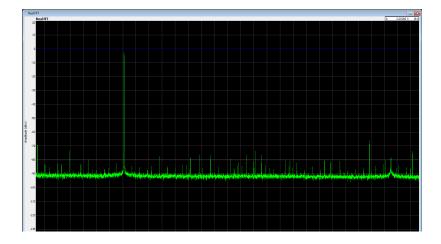

Test Case 2:

Input Frequency: 1842 MHz Input amplitude: -1 dBFS Sample rate: 3.0 GSPS Full Scale: 12.525 dBm

DDC: Decimate-by-4

FFT: 16384 Average: 5 PGA: none

Result >>

Single-tone spurious: -63.125 dBc IMD3: 68.375 dBc @ -8dBFS FFT Noise Level: -81.025 dBm

### UNIT MANAGEMENT

- Autonomous/programmable fan control

- Auto shutdown on fault

- Autonomous voltage/current/fan monitoring and protection

- Fault recording

- Always-on USB access to fault log

- USB/JTAG access to compliant devices throughout

- Serial port interface to Microblaze processor

### PLATFORM MANAGEMENT

- Services on all Ethernet interfaces

- DHCP

- Ping

- Health monitoring

- Network-based FPGA Configuration

- High-speed via 1 GbE or 40 GbE interface (< 1 second)</p>

- Board Support Package provides the code

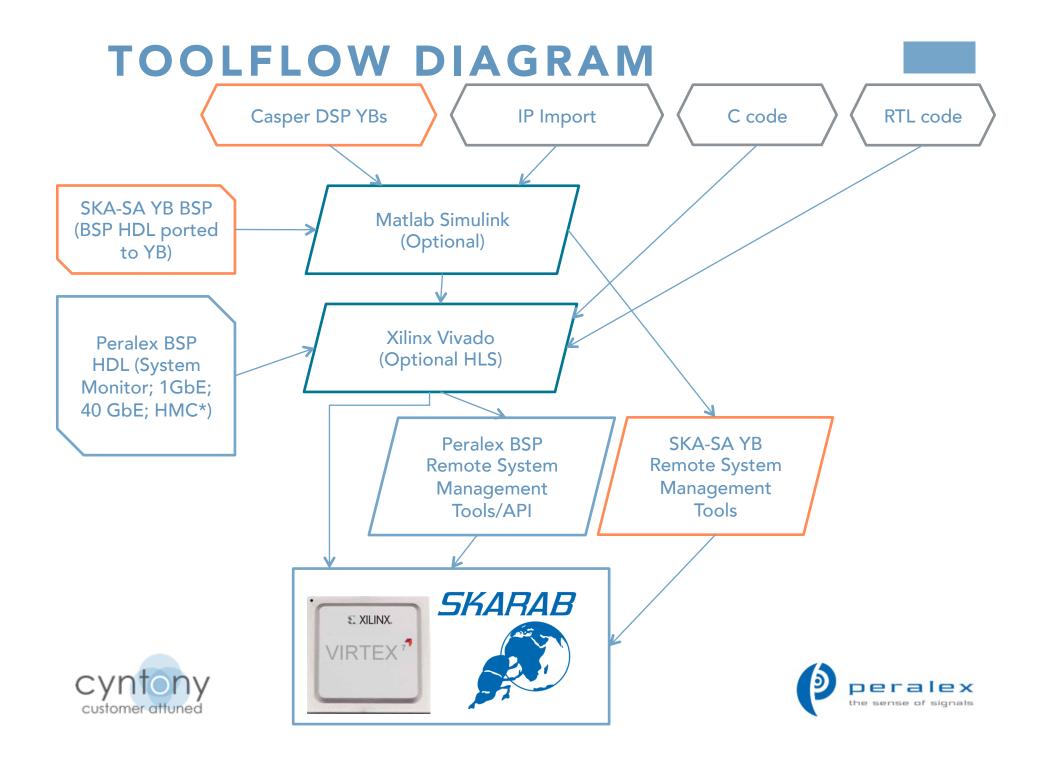

### + SOFTWARE SUPPORT

- Includes open-source Board Support Package (BSP)

- HDL code for Xilinx Vivado suite (customer supplied)

- FPGA Firmware for 1 GbE MAC, 40 GbE MAC & PHY, HMC, ADC

- Microblaze soft-processor, Wishbone peripheral bus and 1-Wire

- Fan control, air speed/thermal/voltage/current monitoring

- Includes Network Management

- Windows/Linux C++ reference code and executables to manage unit(s) via a network-attached PC

- Support for open-source Yellow Blocks and JASPER code via CASPER listsery

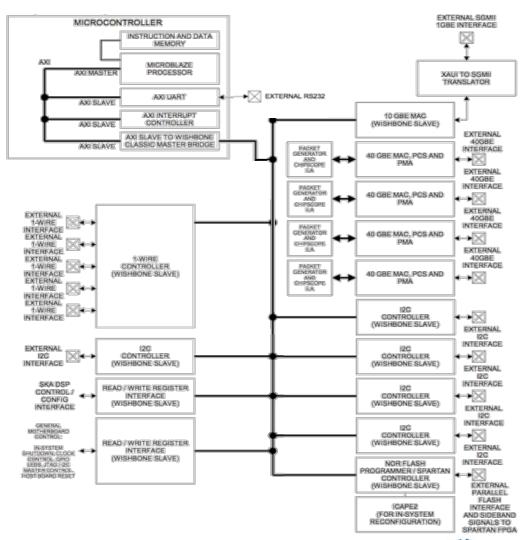

### **BSP BLOCK DIAGRAM**

- Microblaze soft μC

- Wishbone bus/SDRAM

- 10/40 GbE PHY, MAC

- I2C, Register R/W

- FLASH controller

- ICAPE2 configuration

### + ABOUT PERALEX

- Founded 1987, located near Capetown, South Africa

- Pioneer in high-end DSP and SDR

- Designer and manufacturer for sophisticated customers:

- South African National Space Agency, SKA-SA (MeerKAT), CapeRay

- GEW Technologies, L-3 Communications, Cassidian

- High Performance Products

- Wideband radio receivers, FPGA extreme computing

- ADC PCBAs, DSP PCBAs

- Associated firmware and software

- Applications Expertise

- Spectrum Monitoring, Direction Finding, Signal Analysis

# SKARAB IS READY FOR YOUR RESEARCH PROPOSALS NOW

- Mature, fully qualified, in production and shipping

- Over 100 SKARAB systems delivered to SKA-SA for MeerKAT

- CASPER Listserv development support, actively led by SKA-SA

- Board Support Package (BSP) on Github

- Come see the ADC Mezzanine in action in the demo room

### + CONTACT INFORMATION

Cyntony is the premier worldwide distributor for Peralex

- David A Moschella 617-407-0753 dmoschella@cyntony.com

- Cyntony Corporation 195 Follen Road Lexington, MA 02421

cyntony.com